|

||

|

HORARIO: L(8-10: LPSySE), M-M-J (8-9 hrs: A5).

REQUISITOS PARA CURSAR ESTA MATERIA

|

||

| OBJETIVO GENERAL DEL CURSO | ||

|

Objetivos específicos

|

||

| CONTENIDO DEL CURSO | ||

|

|

UNIDAD I PROGRAMACION EN VHDL. 1 .1 Elementos del lenguaje VHDL 1.1.1 Elementos sintácticos del VHDL. 1.1.2 Operadores y expresiones en VHDL 1.1.3 Tipos de datos. 1.1.4 Subtipos de datos 1.2 Declaraciones básicas de objetos 1.2.1 Declaración de constantes 1.2.2 Declaración de variables 1.2.3 Declaración de señales 1.2.4 Declaración de ficheros. 1.3 Declaraciones concurrentes. 1.3.4 Declaración de entidad. 1.3.5 Declaración de arquitectura. 1.3.6 Diferentes tipos de arquitecturas(Estructural, Flujo de datos y Funcional). 1.3.7 Ejemplos de descripción flujo de datos. 1.4 Ejemplos de declaraciones secuenciales 1.4.1 Ejemplos de diagramas de máquinas de estado. 1.5 Funciones y subprogramas 1.5.1 Declaración de procedimientos y funciones 1.5.2 Subprogramas 1.5.3 Paquetes 1.5.4 Bibliotecas 1.6 Programación de FPGA´s o CPLD’S en una aplicación. UNIDAD II. MAQUINAS DE ESTADOS FINITO. 2.1 Modelo de Mealy y Modelo de Moore. 2.2 Representación de los modelos Mealy y Moore en diagramas de estado y diagrama ASM. 2.3 Diseño de máquinas de estados finitos tipo Mealy y tipo Moore utilizando VHDL. 2.3.1 Obtención de la tabla de estados. 2.3.2 Obtención de la tabla de excitación. 2.3.3 Obtención de las ecuaciones de excitación. 2.3.4 Programación de archivo .vhd. 2.3.5 Simulación del archivo .vhd 2.3.6 Obtención del archivo .jed. 2.3.7 Programación del PLD o FPGA. UNIDAD III. MEMORIAS 3.1 Fundamentos de sistemas numéricos. 3.1.1 Sistema de numeración hexadecimal. 3.1.2 Operaciones aritméticas en el sistema hexadecimal. 3.2 Conceptos de memorias. 3.2.1 Terminología de memorias 3.2.2 Operación general de memorias 3.2.3 Tipos de memorias 3.2.4 Estructura interna de una celda memorias 3.2.5 Ciclos de lectura/escritura 3.2.6 Interconexión de memorias 3.2.7 Aplicaciones de memorias en la lógica combinacional y secuencial UNIDAD IV. ARQUITECTURA DE PROCESADORES. 4.1 Estructura y funcionamiento de una ALU. 4.1.1 Registro de estado. 4.1.2 Operaciones con datos de memoria y registros. 4.1.2 Operaciones con punto flotante y fijo. 4.2 Descripción de una ALU con VHDL. 4.3 Arquitectura Von Neumann. 4.3.1 Arquitectura de los Microprocesadores. 4.4 Arquitectura Harvard. 4.4.1 Arquitectura de los Microcontroladores. https://drive.google.com/file/d/1iQ7eIn9b9N3ggZSSzbdSelwgkZvTD34b/view?usp=sharing UNIDAD V. MODULOS DE INTERFAZ EN VHDL. 5.1.

Comunicación serial con UART.

5.1.1.

Introducción.

5.2. Comunicación serial por I2C. 5.1.2. Diseño de un UART en VHDL. 5.2.1.

Introducción a I2C.

5.3. Comunicación por Ethernet utilizando IP cores.5.2.2. Diseño de un módulo para comunicación I2C. 5.2.3. Comunicación de un FPGA con otro dispositivo por medio de I2C. 5.3.1.

Introducción a

Ethernet.

5.4. Comunicación por CAN utilizando IP cores. 5.3.2. Utilización de IP cores para comunicar dos FPGA´s por Ethernet. 5.4.1.

Introducción al Bus

CAN.

5.4.2. Utilización de IP cores para comunicar dos FPGA´s por bus CAN. |

|

| EQUIPOS PARA TRABAJO DE FIN DE CURSO | ||

|

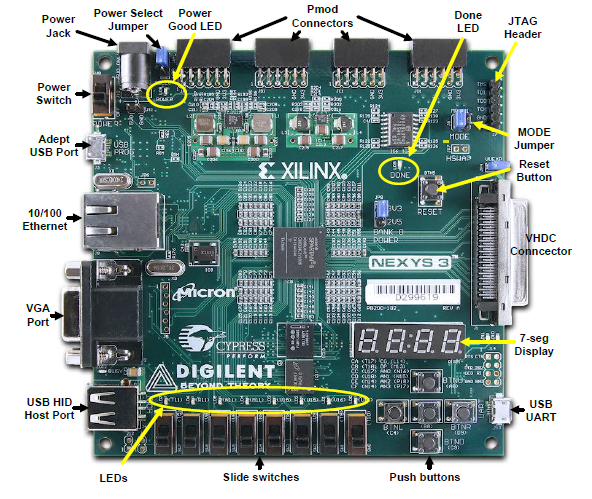

DEVELOPMENT BOARDS AND MATERIAL

FOR LABs.

|

||

|

||

| RECURSOS EXTRAS. | ||

|

VIDEOS TUTORIALES:

1.- VHDL Basics (Intel): WEBSITES DE APOYO

1.- VHDL Coding: Tips and Tricks. 2.- Finite State Machine Designer. 3.- Test Bench Generator for VHDL << video for help>> 4.- EasyEDA. <<What it´s EDA>> 5.- Google colab. 6.- Edaplayground. 7.- VHDL and FPGA terminology: |

||

| REFERENCIAS BIBLIOGRAFICAS Y SITIOS INTERNET | ||

(LIBRO) Fundamentos de Sistemas Digitales, Thomas L. Floyd, Editorial Prentice Hall (LIBRO) Fundamentos de Lógica digital con diseño VHDL, Stephen Brown, Zwonko Vranesic, Editoral Mc Graw hill (reference manual) Nexys3™ Board Reference Manual, Digilent |

||